秋林 做网站自己怎么搭建网站

串并转换器OSERDESE2

可被Select IO IP核调用。

OSERDESE2允许DDR功能

参考:

FPGA原语学习与整理第二弹,OSERDESE2串并转换器 - 知乎 (zhihu.com)

正点原子。

ISERDESE2原语和OSERDESE2原语是串并转换器,他的的功能都是实现串行数据和并行数据之间的转换。

OSERDESE2原语将并行数据转换为串行数据,减少数据传输端口数量的同时也提高了频率,将低速数据转换为高速数据,方便传输。

ISERDESE2原语是将串行数据转换为并行数据,将高速信号转换为低速数据,方便处理。和前面一样,赛灵思官方也给我们提供出来了相应的IP核SelectIO InterfaceWizard,对这些原语进行了封装,提供图形化界面方便使用,我们可以从这些IP来认识这些原语。

OSERDESE2原语包含两个部分,一部分是数据3态控制器,一部分是串并数据转换控制器。

因此我们可以把它们端口分成三大类,一部分是关于三态控制,一部分是关于时钟复位信号,一部分串并数据转换输入输出。在时钟复位信号中,CLK是串行数据时钟,是高速时钟,CLKDIV是并行数据时钟,是低速时钟。在串并数据转换输入输出部分中,D1~D8是并行数据输入,

一个OSERDESE2最高支持8:1串并转换,想要达到更高速率转换,必须采用级联两个OSERDESE2的方式,这个后面重点讲述。OQ是串行数据输出端口。OFB也是输出端口,但是他有特殊的作用,一个是与ISERDESE2上的OFB引脚相连,作为反馈端口,一个是与ODELAYE2相连,作延迟输出使用,这个端口在正常使用过程一般悬空即可。OCE是高速时钟CLK的使能信号,可以一直置高电平,保证高速时钟一直使能。

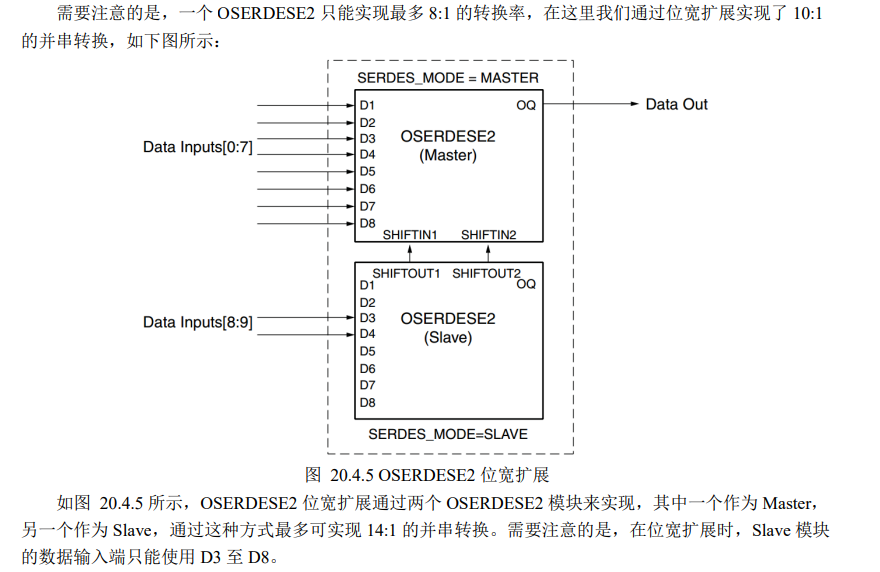

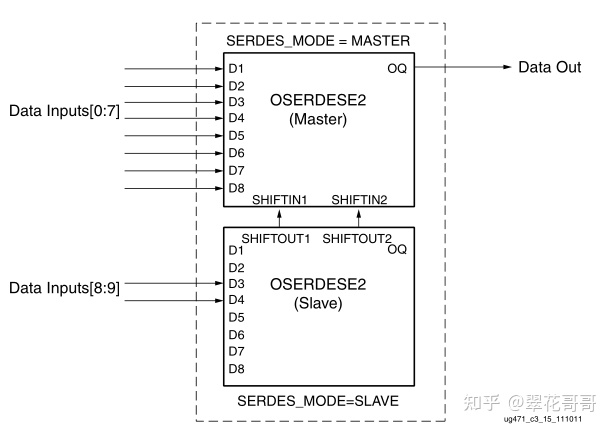

两个OSERDESE2的串联方法

DDR模式下,两个OSERDESE2原语串联方式,其中并行输入数据高2位会传入OSERDESE2原语(slave)D3-D4引脚,而OSERDESE2原语(slave)的SHIFTOUT1和SHIFTOUT2会连到OSERDESE2原语(Master)的SHIFTIN1和SHIFTIN2。

例程:代码来自正点原子

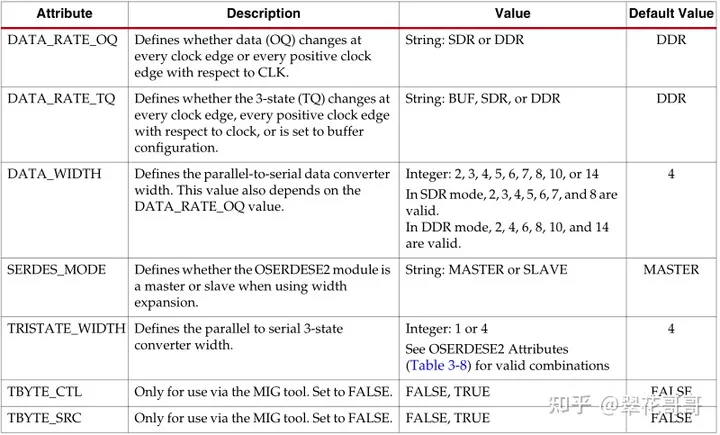

DATA_RATE_OQ是定义串行数据是以DDR的方式传输还是以SDR的方式传输,

DATA_WIDTH是定义并行数据的位宽,

SERDES_MODE是在当需要两个OSERDESE2级联时,可以用于辨识那个是MASTER,那个是SLAVE。

而DATA_RATE_TQ,TRISTATE_WIDTH是关于三态控制的,我们可以不用管。最后两个也是我们大多数情况下用不到的,默认FALSE就好。

//例化OSERDESE2原语,实现并串转换,Master模式

OSERDESE2 #(.DATA_RATE_OQ ("DDR"), // 设置双倍数据速率.DATA_RATE_TQ ("SDR"), // DDR, BUF, SDR.DATA_WIDTH (10), // 输入的并行数据宽度为10bit.SERDES_MODE ("MASTER"), // 设置为Master,用于10bit宽度扩展.TBYTE_CTL ("FALSE"), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE"), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1) // 3-state converter width (1,4)

)

OSERDESE2_Master (.CLK (serial_clk_5x), // 串行数据时钟,5倍时钟频率.CLKDIV (paralell_clk), // 并行数据时钟.RST (reset), // 1-bit input: Reset.OCE (1'b1), // 1-bit input: Output data clock enable.OQ (serial_data_out), // 串行输出数据.D1 (paralell_data[0]), // D1 - D8: 并行数据输入.D2 (paralell_data[1]),.D3 (paralell_data[2]),.D4 (paralell_data[3]),.D5 (paralell_data[4]),.D6 (paralell_data[5]),.D7 (paralell_data[6]),.D8 (paralell_data[7]),.SHIFTIN1 (cascade1), // SHIFTIN1 用于位宽扩展.SHIFTIN2 (cascade2), // SHIFTIN2.SHIFTOUT1 (), // SHIFTOUT1: 用于位宽扩展.SHIFTOUT2 (), // SHIFTOUT2.OFB (), // 以下是未使用信号.T1 (1'b0), .T2 (1'b0),.T3 (1'b0),.T4 (1'b0),.TBYTEIN (1'b0), .TCE (1'b0), .TBYTEOUT (), .TFB (), .TQ ()

);//例化OSERDESE2原语,实现并串转换,Slave模式

OSERDESE2 #(.DATA_RATE_OQ ("DDR"), // 设置双倍数据速率.DATA_RATE_TQ ("SDR"), // DDR, BUF, SDR.DATA_WIDTH (10), // 输入的并行数据宽度为10bit.SERDES_MODE ("SLAVE"), // 设置为Slave,用于10bit宽度扩展.TBYTE_CTL ("FALSE"), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE"), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1) // 3-state converter width (1,4)

)

OSERDESE2_Slave (.CLK (serial_clk_5x), // 串行数据时钟,5倍时钟频率.CLKDIV (paralell_clk), // 并行数据时钟.RST (reset), // 1-bit input: Reset.OCE (1'b1), // 1-bit input: Output data clock enable.OQ (), // 串行输出数据.D1 (1'b0), // D1 - D8: 并行数据输入.D2 (1'b0),.D3 (paralell_data[8]),.D4 (paralell_data[9]),.D5 (1'b0),.D6 (1'b0),.D7 (1'b0),.D8 (1'b0),.SHIFTIN1 (), // SHIFTIN1 用于位宽扩展.SHIFTIN2 (), // SHIFTIN2.SHIFTOUT1 (cascade1), // SHIFTOUT1: 用于位宽扩展.SHIFTOUT2 (cascade2), // SHIFTOUT2.OFB (), // 以下是未使用信号.T1 (1'b0), .T2 (1'b0),.T3 (1'b0),.T4 (1'b0),.TBYTEIN (1'b0), .TCE (1'b0), .TBYTEOUT (), .TFB (), .TQ ()

); 并串转换器ISERDES

(LVDS差分信号简单处理)4. 使用ISERDES接收高速串行数据 - 知乎 (zhihu.com)