平台网站制作公司推广软文代发

本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注www.meyesemi.com)

紫光的logos系列的PGL50H/PGL100H、logos-2全系列都集成gen2×4的PCIE硬核,且官方也提供了例程。

紫光的PCIE用起来还是挺方便的,生成IP的同时生成了对应的PCIE example例程。紫光的PCIE IP虽然没有像xilinx那样可以直接使用Block Design设计,但是仔细读一遍官方例程的DMA模块,进而开发自己的东西,还是能够很好用起来紫光的PCIE。

对于毫无PCIE知识和经验的小白来说,比如我来说,使用好紫光的PCIE还是有难度的。毕竟紫光的参考资料真不多,网上也可以说几乎没有,且官方的IP、说明文档并不是写给小白看的。

对小白来说,很可能一开始和主机怎么交互起来都是一个问题。入门一看PCIE协议,会发现繁多也难懂——PCIE体系庞大足以让天下无书,这夸张我已经不知道从哪里听来了。如果能够一边把PCIE通信交互转起来,一边理解去PCIE协议,那就很容易把pcie协议理解彻透彻,当然这里狭义指的是上层交互的TLP协议,数据链路层和物理层更复杂的事情是硬核做的,用起来PCIE并不需要深入了解。

如何使用紫光PCIE,首先FPGA端需要一个PCIE的例程,这个官方在生成IP的同时就自带生成的。

一、生成官方例程的步骤:

(1)新建一个工程,工程选择对应的芯片型号。

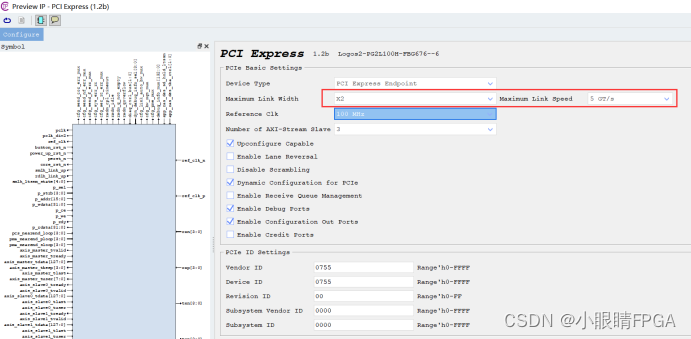

(2)进入IP Compiler,例化一个PCIE IP,注意的是紫光不同系列的PCIE IP并不通用,不同的系列都需要安装不同的PCIE IP包。

(3)参数配置,PCIE 的gen1是2.5GT/s,gen2是5GT/s,芯片集成的是gen2的硬核,所以选5GT/s,link Width看开发板的硬件设计,IP最大支持X4,例程我使用的开发板最大只支持X2,那就选择X2,选择X1也行(理论传输速度慢一倍)。

(4)其他参数默认即可,官方例程默认是打开了3个BAR空间,后面例程会使用BAR0为正常的内存读写,BAR1用于指示DMA读写操作,BAR2映射存储DMA操作的数据。

(5)生成IP后,在file选项选择open project打开官方生成的例程,官方生成工程路径在刚才生成IP工程目录下的..\ipcore\pcie_test\pnr\example_design,只需要打开该目录下的pango_pcie_top.pds工程即可。

(6)打开工程后,理论上可以直接使用了,只要开发板设计好了PCIE链路的,都可直接与主机交互了,因为PCIE的管脚是无需用户物理约束的。但是官方例程的top可以看到还是有除了PCIE的其他信号,这些信号其实是不影响FPGA作为Endpoint与主机的交互,但建议还是根据开发板对应管脚更改一下。特别是ref_led/pclk_led和smlh_link_up/rdlh_link_up这几个信号,这几个信号可以在主机开机时帮助我们判断PCIE链路是否链通。其中ref_led/pclk_led可以表明主机的PCIE接口时钟能够给到FPGA硬核,smlh_link_up/rdlh_link_up可以表明主机与FPGA硬核能够链接成功,link_up后主机内核程序可以读到PCIE的配置空间信息,进而给FPGA的PCIE分配PCIE总线域空间(bar基地址也在初始化给到PCIE硬核配置空间)。

(7)修改好相关信号的引脚分配后,就可以生成bitstream了。

二、使用WinDriver驱动紫光PCIE:

(1)FPGA端的程序可以提前固化好到开发板,然后将开发板固定插在主机主板的PCIE插槽中,此过程在关机状态下完成。

(2)如果硬件PCIE链路设计并没有使用PCIE插槽电源供电开发板,那么开发板需要使用外部电源供电,反之可以选择由PCIE插槽直接供电开发板,然后开机。

(3)开机后,如果链接成功(可通过两个link_up信号指示灯快速判断),打开设备管理器,可以看到一个PCI内存控制器的其他设备,如果没有链接成功,可重新下载固件或者检测硬件连接,注意流程是先下载后开机。

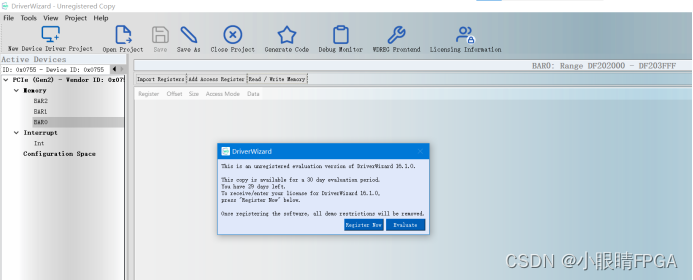

(4)网上下载WinDriver,下载安装流程就不用多说了,官方可以申请一个月的试用。官网下载链接:WinDriver - Device Driver Development Toolkit | Jungo

(5)安装好,可以简单用起来了,这里展示一下对PCIE的BAR0进行内存读写,注意的是官方例程只有BAR0是可以正常内存读写的。

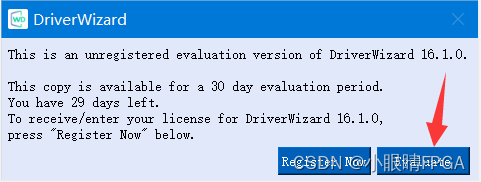

因为在jungo_windriver官网下载的是Evaluate版,所以打开软件直接选择评估版进去。

点击New host driver project进去。

点击New host driver project进去。

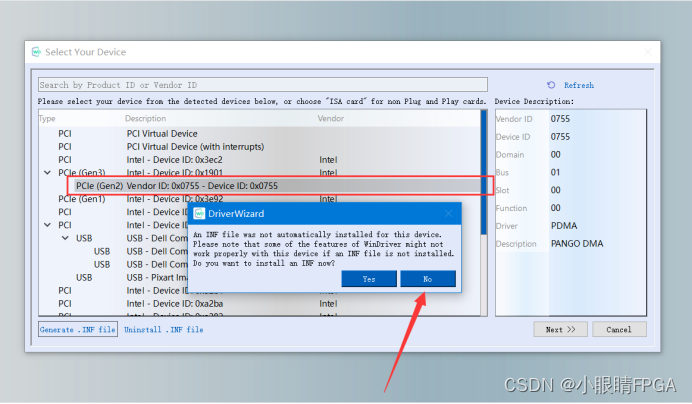

由于只简单用一下,选中紫光PCIE设备(紫光PCIE的ID默认设置都是0x0755)点击进去。

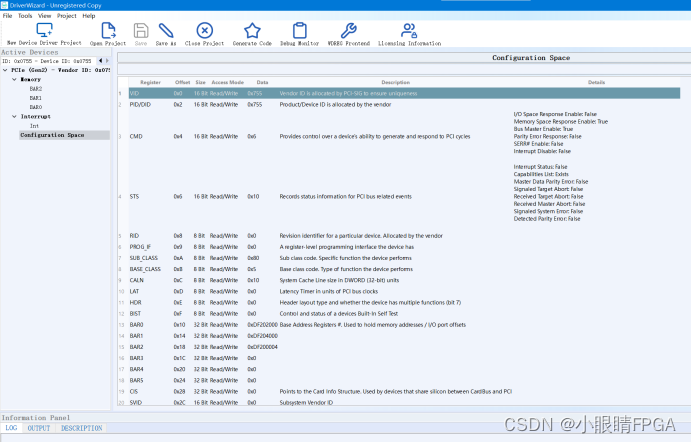

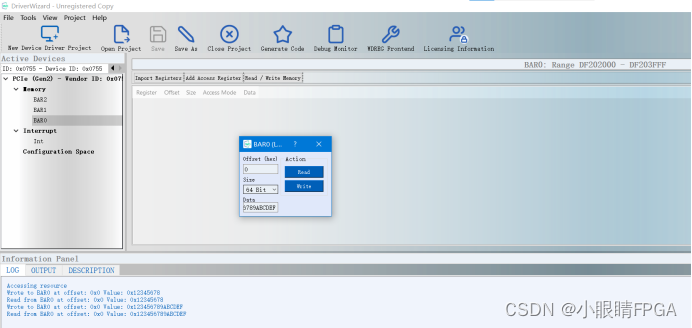

进去后,可以看到PCIE设备的详细信息。

进去后,可以看到PCIE设备的详细信息。

选BAR0,同样选择Evaluate进去。

点击Read/Write Memory,就可以对BAR0映射的内存读写了。

可以看到读写是正确的,也可以通过地址偏移来读写,BAR1和BAR2也可以进行Read/Write Memory,但是由于例程设计的BAR1用于DMA操作指令,BAR2用于DMA数据映射,所以BAR1和BAR2在这里写进去的数据和读出来的数据是不一致的。

(5)使用WinDriver对BAR0写进去和读出来是一致的,但是这样并不知底层如何操作,可以在FPGA使用Inserter抓取相关信号结合PCIE协议来分析。RX信号在axis_master,TX信号在axis_slave,其中例程中axis_slave0是用来发送CplD报文的,axis_slave1是用来发送Mrd报文的,axis_slave2是用来发送Mwr报文的(需要注意的是用哪个slave来发送什么类型TLP,是可以自定义的,理论上什么TLP都可以使用一路slave发送,不过这样需要自己仲裁发送逻辑)。基于WinDriver的的BAR0内存读写可以抓取axis_master组和axis_slave0组来分析上层的TLP协议,至于如何解析接收到TLP和组成发送TLP,需要往例程DMA模块深入解读。

如何利用起来官方例程中的DMA传输数据呢?下回分析。