徐州网站制作seo关键字优化软件

前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载的示例:表决器(三人表决器)。

- 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片

- 配置方式:USB-JTAG/SPI Flash

- 高达100MHz 的内部时钟速度

- 存储器:2Mbit SRAM N25Q064A SPI Flash(样图旧款为N25Q032A)

- 通用IO:Switch :x8LED:x16Button:x5DIP:x8 通用扩展IO:32pin

- 音视频/显示: 7段数码管:x8 VGA视频输出接口 Audio音频接口

- 通信接口:UART:USB转UART Bluetooth:蓝牙模块

- 模拟接口: DAC:8-bit分辨率 XADC:2路12bit 1Msps ADC

目录

Ⅰ. 前置知识

0x00 表决器

0x01 真值表表示

0x02 卡诺图表示

0x03 逻辑表达式:

Ⅱ. Verilog实现

0x00 新建工程并添加的IP包

0x01 利用IP器件创建电路

0x02 Test Bench——添加仿真激励文件

0x03 仿真记录与分析

Ⅲ. 解释说明

Ⅰ. 前置知识

0x00 表决器

以三人表决器为例说明多人表决电路的原理。

设三人表决器中输入为A、B、C,同意用1表示,不同意用0表示。输出为F,A、B、C三者中多数同意,提案通过,否则提案不被通过;通过用1表示,不通过用0表示。

0x01 真值表表示

| 输入 | 输出 | ||

| A | B | C | F |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

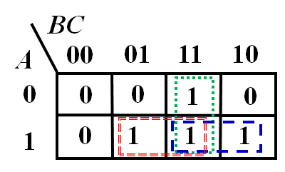

0x02 卡诺图表示

0x03 逻辑表达式

过程:写输出表达式即把输出结果为一的输入相加。如上F的一的有四个,把结果为一对应的输入写出即可,再化简,可通过卡诺图以及逻辑表达式化简。

可用狄摩根律转化为与非形式

若此步有不清楚的可留言

Ⅱ. Verilog实现

在本次Verilog实现表决器的功能中,我们学习如何利用他人封装好的组件型IP器件进行设计,故选择为工程添加所需IP包的方法。

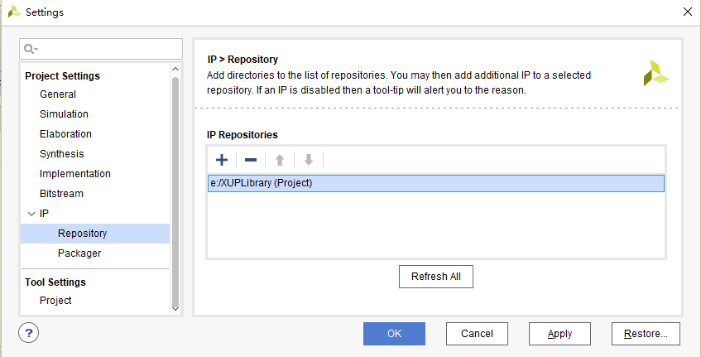

0x00 新建工程并添加的IP包

在工程settings中IP的Repository中选择所需IP包的存放目录

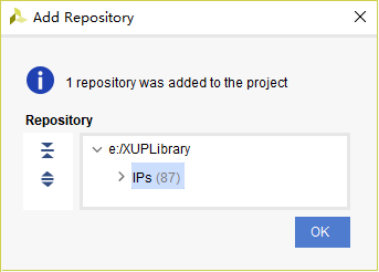

点击Select,在图所示对话框中点击ok

Repositories自动更新如图:

点击OK完成IP包的添加

0x01 利用IP器件创建电路

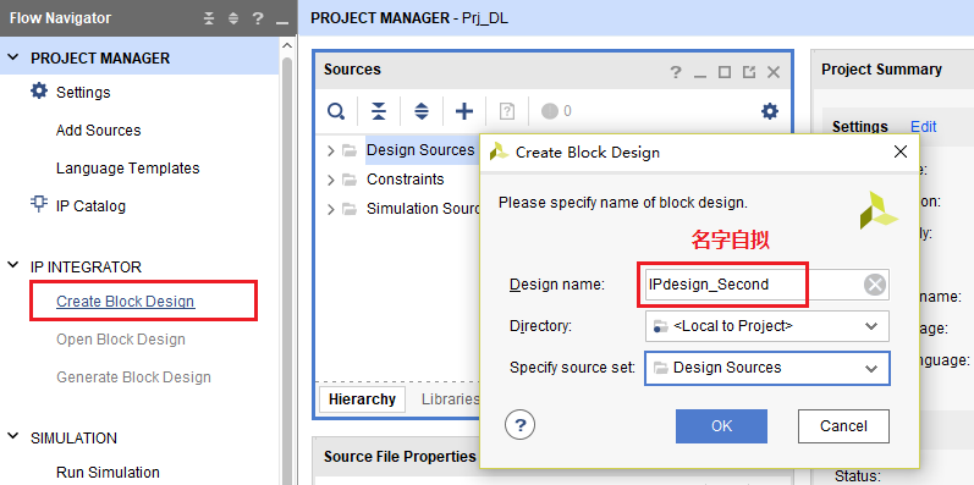

点击Flow Navigator中的IP INTEGRATOR下Create Block Design,为电路设计命名:

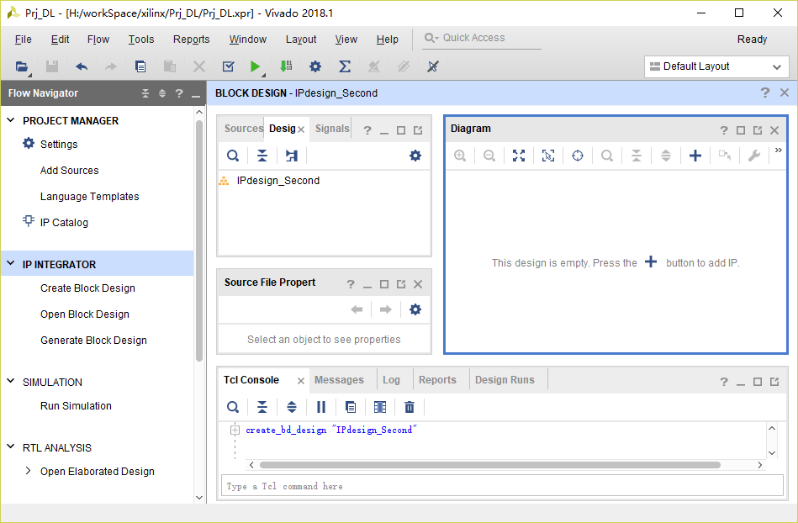

点击OK后工程自动更新至如图:

在Diagram窗中点击![]() 按钮,添加IP器件。

按钮,添加IP器件。

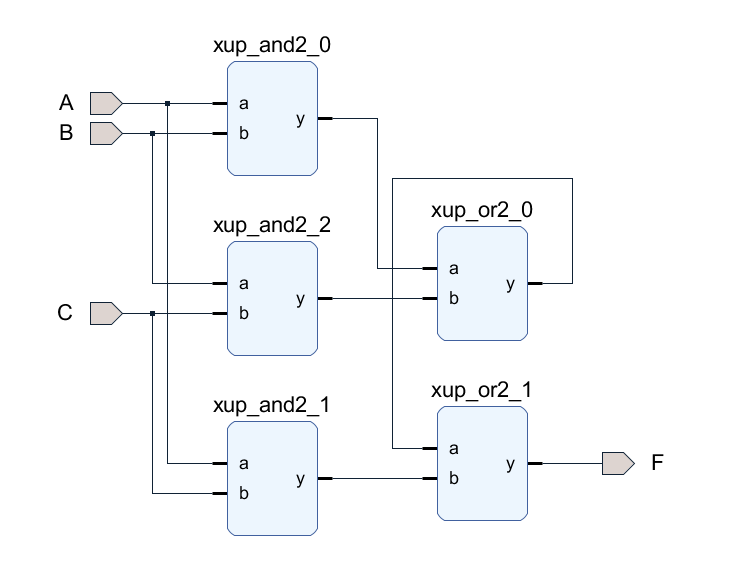

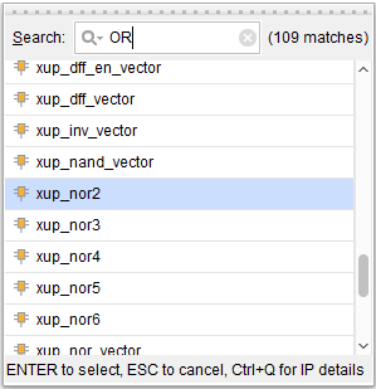

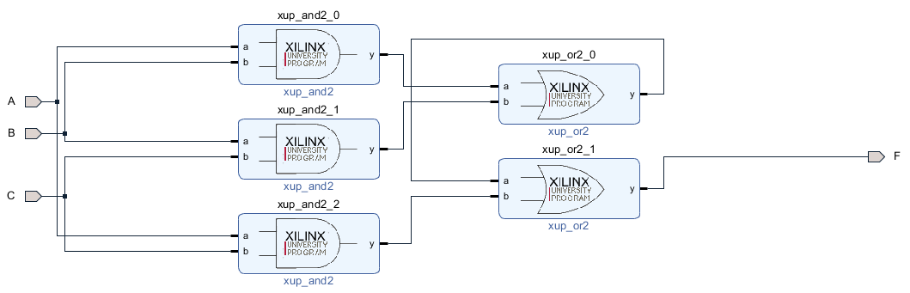

根据原理中的F=AB+BC+CA,本实验添加两种基本器件:AND和OR,

如图:

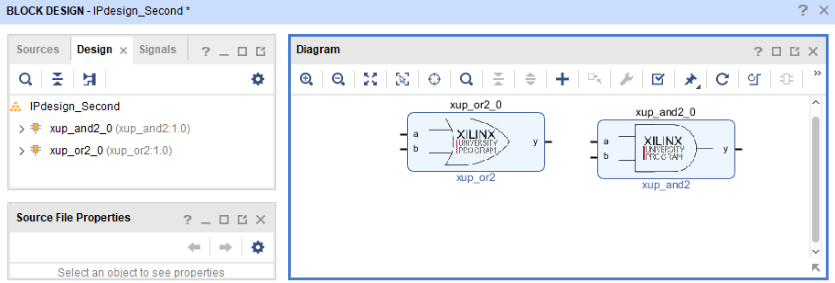

完成后Design窗自动更新至下图效果:

在Diagram窗,完成器件添加

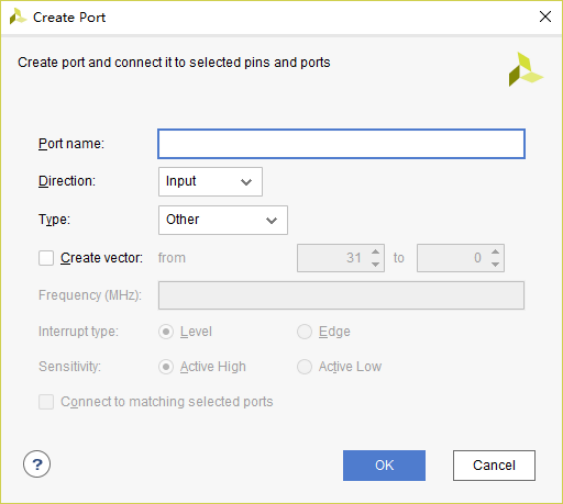

之后添加基本引脚:

增加输入引脚3个,命名自拟

可以为A、B、C,输出1个,可以命名为F。

完成连线,如图:

点击![]() 检查布线的正确性

检查布线的正确性

另外,可点击![]() 可以自动优化布线,但这一步并不是必须的

可以自动优化布线,但这一步并不是必须的

可得出下图:

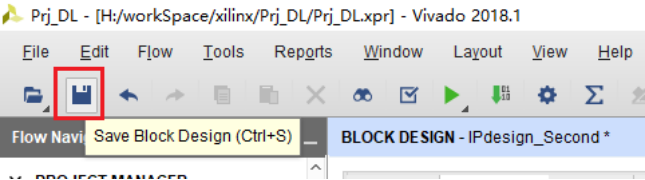

点击【保存】按钮,保存电路设计文件:

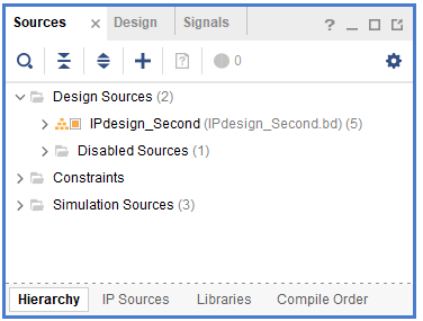

在Sources栏可以看到新增的文件如图:

点击该新增文件,如图:

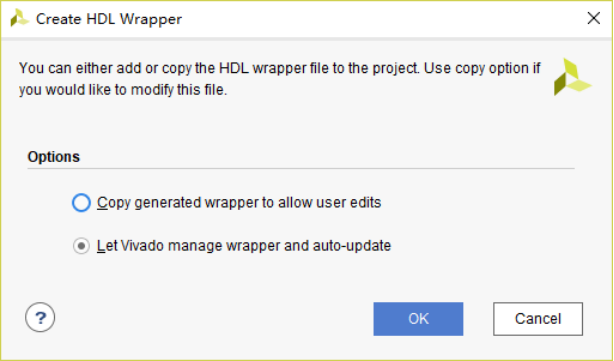

点击Create HDL Wrapper菜单。利用默认项,可让Vivado自动生成代码,如图:

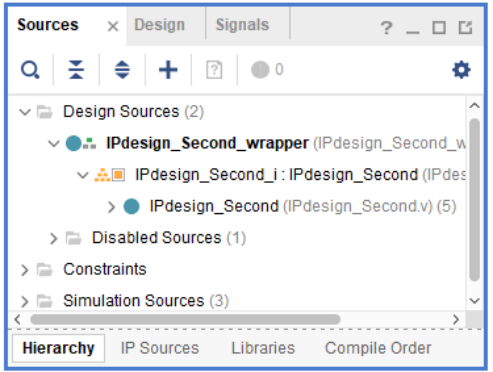

Source栏会自动更新至如图效果:

0x02 Test Bench——添加仿真激励文件

`timescale 1ns / 1ps

module sim4Second( );

reg inA;reg inB;reg inC;

wire outF;

IPdesign_Second_wrapper test(.A(inA),.B(inB),.C(inC),.F(outF));

always begininA = 0;inB = 0;inC=0; #100;inA = 0;inB = 0;inC=1; #100;inA = 0;inB = 1;inC=0; #100;inA = 0;inB = 1;inC=1; #100;inA = 1;inB = 0;inC=0; #100; inA = 1;inB = 0;inC=1; #100;inA = 1;inB = 1;inC=0; #100;inA = 1;inB = 1;inC=1; #100;end

endmodule0x03 仿真记录与分析

| 输入 | 输出 | ||||

| 周期 | 时间 | A | B | C | F |

| 1 | 0-100ns | 0 | 0 | 0 | 0 |

| 2 | 100ns-200ns | 0 | 0 | 1 | 0 |

| 3 | 200ns-300ns | 0 | 1 | 0 | 0 |

| 4 | 300ns-400ns | 0 | 1 | 1 | 1 |

| 5 | 400ns-500ns | 1 | 0 | 0 | 0 |

| 6 | 500ns-600ns | 1 | 0 | 1 | 1 |

| 7 | 600ns-700ns | 1 | 1 | 0 | 1 |

| 8 | 700ns-800ns | 1 | 1 | 1 | 1 |

Ⅲ. 解释说明

本篇博客旨在学习如何利用他人封装好的组件型IP器件进行设计,从而理解在vivado中,Block Design仅仅是用以设计的直观,最终还是需要生成Verilog等硬件描述语言后才能进一步完成后续设计。

同时,本实验中,生成的IPdesign_Second_wrapper这个module其实是调用了IPdesign_Second,这种调用属于模块化设计方法,因此仿真激励文件中语句IPdesign_Second_wrapper test(参数); 其实信号会继续传递给IPdesign_Second 子模块; 请在仿真界面中调出不同模块的引脚波形进行观察理解。

若不使用导入IP包的方法,设计文件可书写如下:

`timescale 1 ps / 1 psmodule design_1_wrapper(A,B,C,F);input A;input B;input C;output F;wire A;wire B;wire C;wire F;design_1 design_1_i (.A(A),.B(B), .C(C),.F(F));

endmodule