网站建设360元起全包前端开发

今天的项目是在 Verilog HDL 中实现可编程数字延迟定时器。完整呈现了延迟定时器的 Verilog 代码。

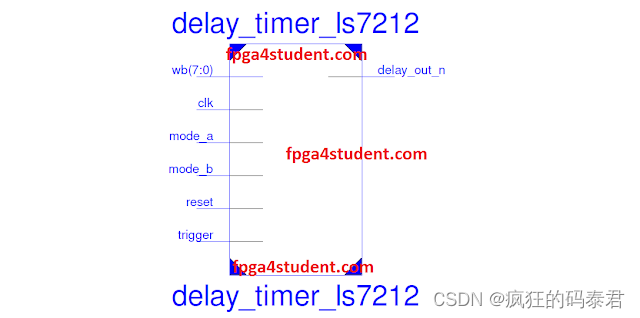

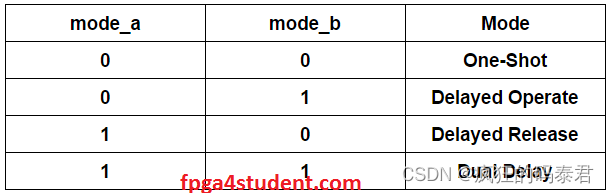

所实现的数字延迟定时器是 CMOS IC LS7212,用于生成可编程延迟。延迟定时器的规格可以在这里轻松找到。基本上,延迟定时器有 4 种操作模式:一次性 (OS)、延迟操作 (DO)、延迟释放 (DR)、双延迟 (DD)。这四种模式将通过输入 mode_a 和 mode_b 选择。

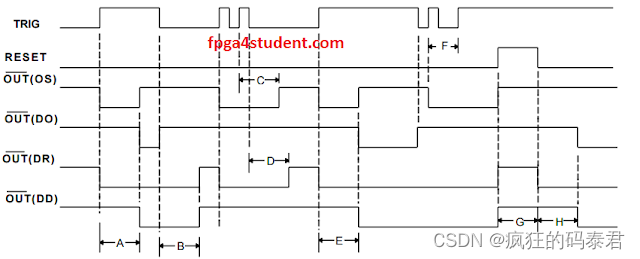

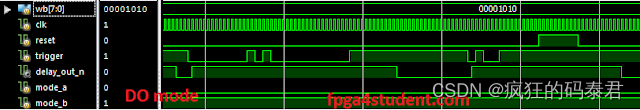

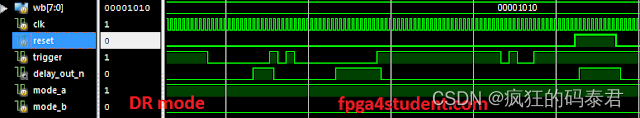

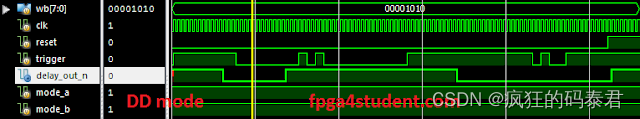

wb[7:0] 输入用于根据延迟定时器规范中给定的方程对延迟进行编程。要了解更多它在每种模式下的工作原理以及输入如何控制延迟,请参阅其数据表。以下波形显示了每种模式下延迟的产生方式。

以下是可编程数字延迟定时器 LS7212 的 Verilog 代码。

//fpga4student.com: FPga projects, Verilog projects, VHDL projects// Verilog project: Verilog code for delay timer LS7212 module delay_timer_ls7212 ( input [7:0] wb, // weighting bits input clk, // clock inputinput reset, // timer reset input trigger, // trigger input input mode_a, mode_b, // mode bits A and B output reg delay_out_n // delay output, active low ); reg[7:0] PULSE_WIDTH ; reg [7:0] DELAY; reg [7:0] TIMER=0; reg trigger_sync_1=0,trigger_sync_2=0; wire trigger_rising,trigger_falling; reg timer_start=0,out_low=0; wire timer_clear2,timer_clear3,timer_clear; reg [1:0] mode; reg reset_timer1=0,reset_timer2=0,reset_timer=0; wire reset_timer3,reset_det; reg reset_det1=0,reset_det2=0;

//fpga4student.com: FPga projects, Verilog projects, VHDL projectsalways @(posedge clk) begin trigger_sync_1 <= trigger; // the first Flip-Flop trigger_sync_2 <= trigger_sync_1;// the second Flip-Flop reset_timer1 <= reset_timer; reset_timer2 <= reset_timer1; reset_det1 <= reset; reset_det2 <= reset_det1; end // Identify the zero to one transitions on trigger signal assign trigger_rising = trigger_sync_1 & (~trigger_sync_2); assign trigger_falling = trigger_sync_2 & (~trigger_sync_1); assign reset_timer3 = reset_timer1 & (~reset_timer2); assign reset_det = reset_det2 & (~reset_det1); // sample Mode and wb always @(trigger_rising,trigger_falling,mode_a,mode_b,wb) begin if(trigger_falling == 1 || trigger_rising == 1) begin PULSE_WIDTH = wb; DELAY = (2*wb + 1)/2; mode = {mode_a,mode_b}; end end // modes always @(mode,reset,trigger_falling,trigger_rising,TIMER,reset,trigger,PULSE_WIDTH,DELAY,reset_det) begin case(mode) 2'b00: // One-Shot Mode begin if(reset) begin out_low <= 0; timer_start <= 0; reset_timer <= 1; end else if(trigger_rising==1) begin out_low <= 1; timer_start <= 1; reset_timer <= 1; end else if(TIMER>=PULSE_WIDTH) begin out_low <= 0; timer_start <= 0; reset_timer <= 1; end end 2'b01: // Delayed Operate Mode begin if(reset) begin out_low <= 0; timer_start <= 0; reset_timer <= 1; end else if(reset_det==1 && trigger==1) begin timer_start <= 1; reset_timer <= 0; end else if(trigger_rising==1) begin timer_start <= 1; reset_timer <= 0; end else if(trigger_falling==1 || trigger == 0) begin out_low <= 0; reset_timer <= 1; timer_start <= 0; end else if(TIMER >= DELAY) begin out_low <= 1; timer_start <= 0; reset_timer <= 1; end //else // reset_timer <= 0; end 2'b10: // Delayed Release Mode begin if(reset) begin out_low <= 0; timer_start <= 0; reset_timer <= 1; end else if(trigger_rising==1 || trigger == 1) begin out_low <= 1; end else if(trigger_falling==1 ) begin timer_start <= 1; reset_timer <= 0; end else if(TIMER>=DELAY) begin out_low <= 0; timer_start <= 0; reset_timer <= 1; end end 2'b11: // Delayed Dual Mode begin if(reset) begin out_low <= 0; timer_start <= 0; reset_timer <= 1; end else if(reset_det==1 && trigger==1) begin timer_start <= 1; reset_timer <= 0; end else if(trigger_falling==1 || trigger_rising==1 ) begin timer_start <= 1; reset_timer <= 0; end else if(TIMER>=DELAY) begin out_low <= trigger; timer_start <= 0; reset_timer <= 1; end end endcase end

//fpga4student.com: FPga projects, Verilog projects, VHDL projects// timer always @(posedge clk or posedge timer_clear) begin if(timer_clear) TIMER <= 0; else if(timer_start) TIMER <= TIMER + 1; end assign timer_clear = reset_timer3 | trigger_rising == 1 | timer_clear3 ; assign timer_clear2 = (trigger_rising == 1)|(trigger_falling == 1); assign timer_clear3 = timer_clear2 & (mode == 2'b11); //delay output always @(posedge clk) begin if(out_low == 1) delay_out_n <= 0; else delay_out_n <= 1; end endmodule

延迟定时器的 Testbench Verilog 代码:

`timescale 1ns / 1ps

//fpga4student.com: FPga projects, Verilog projects, VHDL projects

// Testbench Verilog code for delay timermodule tb_ls7212; // Inputs reg [7:0] wb; reg clk; reg reset; reg trigger; reg mode_a; reg mode_b; // Outputs wire delay_out_n; //fpga4student.com: FPga projects, Verilog projects, VHDL projects// Instantiate the Unit Under Test (UUT) delay_timer_ls7212 uut ( .wb(wb), .clk(clk), .reset(reset), .trigger(trigger), .mode_a(mode_a), .mode_b(mode_b), .delay_out_n(delay_out_n) ); initial begin // Initialize Inputs wb = 10; mode_a = 0; mode_b = 0; reset = 0; trigger = 0; #500; trigger = 1; #15000; trigger = 0; #15000; trigger = 1; #2000; trigger = 0; #2000; trigger = 1; #2000; trigger = 0; #20000; trigger = 1; #30000; trigger = 0; #2000; trigger = 1; #2000; trigger = 0; #4000; trigger = 1; #10000; reset = 1; #10000; reset = 0; // Delay Operate // Add stimulus here end initial begin clk = 0; forever #500 clk = ~clk; end endmodule

//fpga4student.com: FPga projects, Verilog projects, VHDL projects

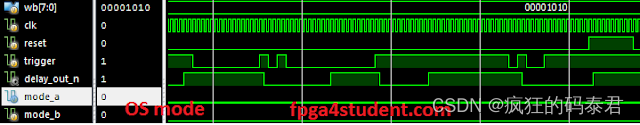

Verilog 中数字延迟定时器的仿真波形

One-Shot Mode

Delayed Operate Mode

Delayed Release Mode

Delay Dual Mode

可编程延迟定时器的 Verilog 代码是可综合的,并且可以在 FPGA 上实现。