做旅游行程的网站百度账号登录

相关阅读

Verilog基础![]() https://blog.csdn.net/weixin_45791458/category_12263729.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12263729.html?spm=1001.2014.3001.5482

“避免在一个always块中混杂阻塞赋值和非阻塞赋值”,这条原则是著名的Verilog专家Cliff Cummings在论文SUNG2000中提出的,这个观点在公众讨论时受到了广泛的质疑。有人认为可以在时钟沿触发的always块里把组合逻辑的阻塞赋值和时序逻辑的非阻塞逻辑安全地混杂在一起。诚然,但是这种编码风格有以下几点不足。

- 这种always块的事件调度理解起来比较费劲。

- 这种always块内的非阻塞赋值应该放在最后。

- 在零延迟的RTL模型中,触发器的输入信号(临时变量)和对应的触发器输出会在同一个时钟沿变化,这种波形令人困惑。

下面来看一下段简单的代码,它拥有正确的代码风格,即没有把阻塞赋值和非阻塞赋值混杂在一起。

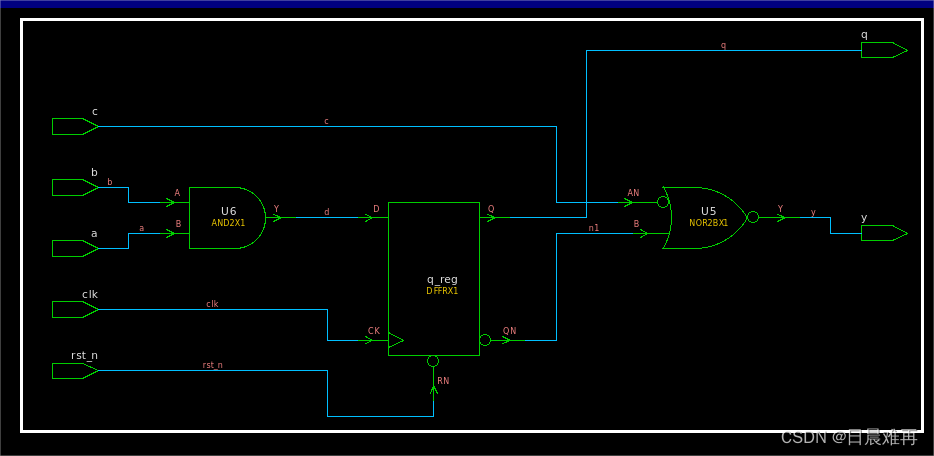

module test(output reg q,output y,input a, b, c, clk, rst_n);wire d;always@(posedge clk or negedge rst_n)if(!rst_n) q <= 0;else q <= d;assign d = a & b;assign y = q & c;endmodule以上Verilog代码的综合结果如图1所示。

图1 对应的综合电路

图1 对应的综合电路

虽然下面的代码也正确地构建上面的电路,但是这段代码把阻塞和非阻塞赋值混杂在同一个always块中。这种编码风格经常被那些具有VHDL背景的工程师采用,因为他们为了提高VHDL仿真性能,习惯于把变量和信号赋值混杂在用一个process块中,但是在Verilog中使用这种风格并不会提高仿真性能。

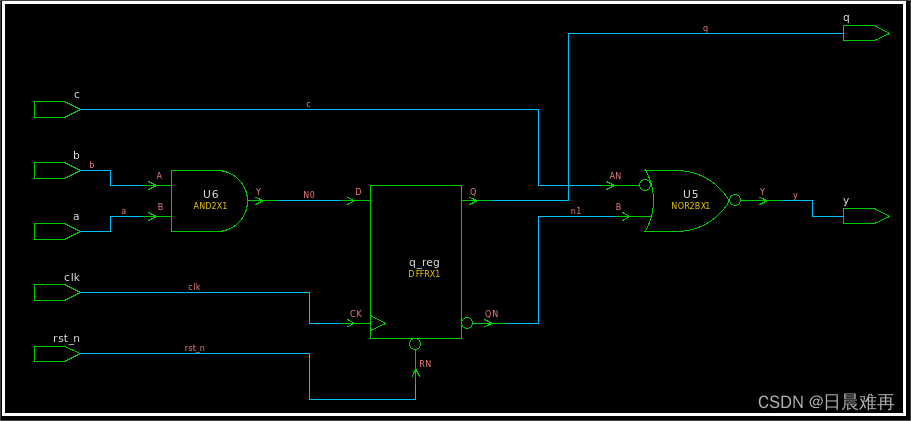

module test(output reg q,output y,input a, b, c, clk, rst_n);always@(posedge clk or negedge rst_n)if(!rst_n) q <= 0;else begin:logicreg d;d = a & b;q <= d;endassign y = q & c;endmodule以上Verilog代码的综合结果如图2所示。

图2 对应的综合电路

图2 对应的综合电路

虽然这段代码在仿真和综合时都正确,但是最好还是不要使用这种编码风格,因为仿真波形会让人困惑。这种混杂的编码风格意味着:当与非门的输入发生变化时,组合信号d不会发生变化,组合信号d发生变化的唯一时刻是在时钟的有效沿或复位。对于大型的设计,工程师要花费很多时间去理解这种怪异的行为——触发器的输入和对应的输出在同一个沿变化,这在真实的硬件上是不会发生的,只是这种编码风格产生的副作用。

除此之外,为了定义内部信号,需要有一个命名块(在上面为logic)。

有的工程师说:对于上述混杂的Verilog代码,当非阻塞赋值用完内部信号后,就把它们赋值为x,这样就不会有人在波形上查看这些内部信号,也不会让人糊涂。下面就是使用这种奇怪编码风格后的代码。对于这种编码风格,内部信号在整个仿真过程中都显示成x,即使他们具有暂时的中间值。为了使用这种不好的编码风格,就制造了这么多的麻烦。

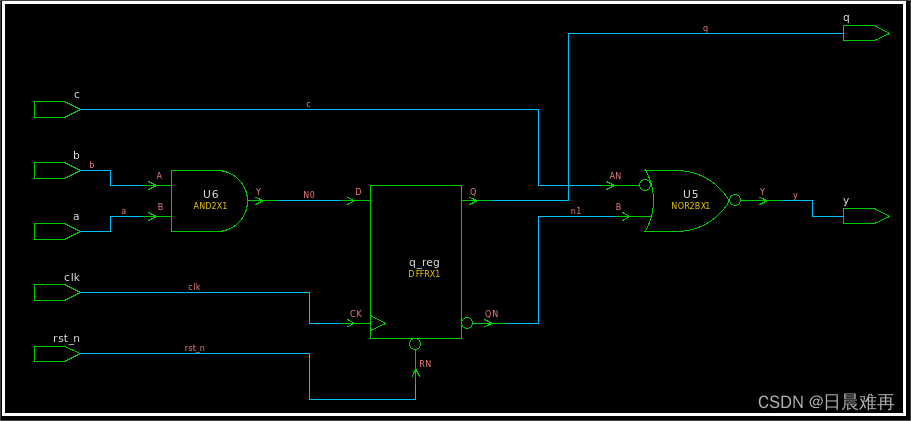

module test(output reg q,output y,input a, b, c, clk, rst_n);always@(posedge clk or negedge rst_n)if(!rst_n) q <= 0;else begin:logicreg d;d = a & b;q <= d;d <= 1'bx;endassign y = q & c;endmodule以上Verilog代码的综合结果如图3所示。

图3 对应的综合电路

图3 对应的综合电路

我们可以看到这种在同一个always块内混杂阻塞和非赋值赋值的编码风格有的缺点:仿真性能差,可读性差(需要对Verilog事件调度有很好的理解),不容易编码(可能以错误的方式混杂了两种赋值,波形令人困惑)。这种风格并没有什么明显的优点,所以Cliff Cummings坚持认为不要在同一个always块中混杂两种赋值。